# **NAPA** User's Guide

Version **4.50**, July 6, 2025

Yves Leduc Greg C. Warwar Richard K. Hester

# **Table Content**

| INTRODUCTION                                                              | 8  |

|---------------------------------------------------------------------------|----|

| THE NAPA COMPILER                                                         | 8  |

| NAPA IDENTIFIERS.                                                         |    |

| NAPA ITERATIVE IDENTIFIERS                                                |    |

| NAPA INSTRUCTIONS                                                         | 9  |

| COMMENTS                                                                  | 10 |

| Nodes or Variables ?                                                      | 10 |

| THE CONCEPT OF NAPA                                                       | 11 |

| THE NAPA NODE                                                             | 11 |

| THE NAPA NETLIST                                                          | 12 |

| THE SAMPLING FREQUENCY                                                    | 12 |

| THE NETLIST PROCESSING                                                    | 14 |

| HANDLING THE DELAYS                                                       |    |

| NODE DETERMINATION AND SORTING                                            |    |

| The Netlist to $C$ Translation                                            |    |

| THE SIMULATION CONTROL                                                    |    |

| NAPA IN A COMPUTER NETWORK                                                |    |

| NAPA COMPILER COMMAND LINE                                                |    |

| NAPA PORTABILITY                                                          |    |

| C LIMITATIONS: IMPORTANT WARNINGS!                                        |    |

| C CASTING: IMPORTANT WARNINGS!                                            |    |

| NAPA PROCESS FLOW                                                         |    |

| THE NAPA FILE SYSTEM                                                      |    |

| 1. Absolute Reference                                                     |    |

| 2. Generic Library Reference                                              |    |

| 3. Root Directory Reference                                               |    |

| 4. Main Directory Reference                                               |    |

| 5. Current Cell Directory Reference  DIRECTORY DEFINITIONS AND PROCESSING |    |

| BEST PRACTICES                                                            |    |

|                                                                           |    |

| NAPA INSTRUCTIONS                                                         | 24 |

| NAPA NODES                                                                | 27 |

| USAGE                                                                     | 27 |

| CHAMELEONIC NODES                                                         | 27 |

| Nodesets                                                                  | 28 |

| PSEUDO-NODES                                                              | _  |

| Unnamed and Unused Signals                                                |    |

| AUTOMATIC NODES                                                           |    |

| BIT FIELD EXTRACTOR                                                       |    |

| NODE KIND LIST                                                            |    |

| NAPA USER'S VARIABLES                                                     | 33 |

| USAGE                                                                     | 33 |

| VARIABLE TYPE                                                             | 33 |

| REGISTER ARITHMETIC                                                       | 35 |

| WIDTH LIMITED NODES AND VARIABLES                                         | 35 |

| LIST OF NAPA INSTRUCTIONS                                                 | 38 |

| ALIAS                          | 38 |

|--------------------------------|----|

| ARRAY                          | 38 |

| ASSERT                         | 40 |

| CALL                           |    |

| COMMAND_LINE                   |    |

| COMMENT                        | 43 |

| DATA                           | 43 |

| DEBUG                          | 45 |

| DECIMATE                       | 45 |

| DECLARE                        |    |

| DIRECTIVE                      |    |

| DROP                           | 49 |

| DUMP                           | 50 |

| DVAR, IVAR                     | 51 |

| ERROR                          | 52 |

| EVENT                          | 52 |

| EXPORT                         | 52 |

| FORMAT                         | 54 |

| FS                             | 55 |

| GANGING                        | 55 |

| GATEWAY                        | 57 |

| HEADER                         | 57 |

| INIT                           | 58 |

| INJECT                         | 60 |

| INPUT                          | 60 |

| CELL INTERFACE, DATA INTERFACE | 61 |

| INTERLUDE                      | 61 |

| INTERPOLATE                    | 62 |

| IVAR                           | 63 |

| LOAD                           | 63 |

| NAPA VERSION                   | 63 |

| NODE                           | 64 |

| NOMINAL                        | 65 |

| NUM INITIAL                    | 65 |

| OPCODE                         | 65 |

| OUTPUT                         | 66 |

| PING                           | 68 |

| POST                           | 69 |

| RANDOM_SEED                    | 70 |

| RESTART                        |    |

| STRING                         | 71 |

| STUCK                          | 72 |

| SYNCHRONIZE                    | 72 |

| TERMINATE                      | 73 |

| TITLE                          | 73 |

| TOOL                           | 74 |

| TS                             | 74 |

| UPDATE                         | 75 |

| VOID                           | 77 |

| WARNING                        | 77 |

| # (COMMENT)                    | 77 |

|                                |    |

| INSTRUCTION QUALIFIERS         | /8 |

| AFTER, BEFORE                  | 78 |

| WHEN                           |    |

| WITH                           | 79 |

| (EXPAND)   (NOEXPAND)                                                      | 80 |

|----------------------------------------------------------------------------|----|

| (NEGATIVE)   (POSITIVE)   (DUAL)                                           | 80 |

| (NO)   (YES)                                                               | 81 |

| (NOCHECK)                                                                  | 81 |

| (HEX)                                                                      | 81 |

| (DIGITAL)                                                                  | 81 |

| (ANALOG)                                                                   | 81 |

| (STRING)                                                                   |    |

| (CONSTANT)                                                                 |    |

| (TRUE)                                                                     | 82 |

| (ARITHMETIC)   (GEOMETRIC)   (HARMONIC)   (RMS)                            |    |

| (POINTER)                                                                  |    |

| (NEW)                                                                      |    |

| ( <option>[::<parm>])</parm></option>                                      |    |

| ( <real output="" scaling="" type="">)</real>                              |    |

| ( <integer_type_output_configuration>)</integer_type_output_configuration> |    |

| SHORT FORMS                                                                |    |

| &UPDATE                                                                    | 85 |

| &CONSTANT                                                                  |    |

| &EXPORT                                                                    |    |

| &DELAYED                                                                   |    |

| SPECIAL SYMBOLS                                                            |    |

| \$                                                                         |    |

| <i>j</i>                                                                   |    |

| √                                                                          |    |

|                                                                            |    |

| <>                                                                         |    |

| ()                                                                         |    |

| #                                                                          |    |

|                                                                            |    |

|                                                                            |    |

|                                                                            |    |

|                                                                            |    |

| :                                                                          |    |

| :                                                                          | 88 |

| NODE KINDS                                                                 | 89 |

| ADC: N LEVELS SIGNED A/D CONVERTER                                         | 89 |

| ALGEBRA: CHAMELEONIC $C$ EXPRESSION                                        |    |

| ALU: USER-DEFINED ALU                                                      |    |

| AND: N INPUTS AND ELEMENT                                                  |    |

| AVERAGE: AVERAGE OF N INPUTS                                               |    |

| BSHIFT: BARREL SHIFTER                                                     |    |

| BTOI: N BITS CONVERSION TO UNSIGNED INTEGER                                |    |

| BUFFER: NON INVERTING BUFFER                                               |    |

| BWAND: N INPUTS BIT WISE AND                                               |    |

| BWBUFFER: BIT WISE NON INVERTING BUFFER                                    |    |

| BWINV: BIT WISE INVERTER                                                   |    |

| BWNAND: N INPUTS BIT WISE NAND                                             |    |

| BWNOR: N INPUTS BIT WISE NOR                                               |    |

| BWNOT: BIT WISE BIT WISE NOT                                               |    |

| BWOR: N INPUTS BIT WISE OR                                                 |    |

| BWXNOR: N INPUTS BIT WISE XNOR                                             |    |

| BWXOR: N INPUTS BIT WISE XOR                                               | 95 |

| CELL: SUB CIRCUIT INSTANTIATION FROM A FILE              | 95   |

|----------------------------------------------------------|------|

| CHANGE: WATCHDOG                                         | 96   |

| CLIP: CLIP ELEMENT                                       | 97   |

| CLOCK: DIGITAL CLOCK GENERATOR                           | 97   |

| COMP: COMPARATOR                                         | 97   |

| CONST: CONSTANT                                          | 98   |

| COPY: SIGNED COPY                                        | 98   |

| COSINE: COSINE WAVE VOLTAGE GENERATOR                    | 99   |

| DAC: N LEVELS SIGNED D/A CONVERTER                       | 99   |

| DALGEBRA: C EXPRESSION CAST TO REAL TYPE                 |      |

| DC: DC VOLTAGE SOURCE                                    | 100  |

| DELAY: SINGLE OR MULTIPLE DELAY                          |      |

| DIFFERENTIATOR: NON INVERTING DIFFERENTIATOR.            |      |

| DIV: DIVIDER ELEMENT                                     |      |

| DTOI: CONVERTS AN ANALOG TYPE NODE TO DIGITAL TYPE       |      |

| DTOOL: USER-DEFINED TOOL                                 |      |

| DUSER: USER-DEFINED FUNCTION                             |      |

| EQUAL: EQUALITY                                          |      |

| FZAND: N INPUTS AND ELEMENT (FUZZY LOGIC)                |      |

| FZBUFFER: NON INVERTING BUFFER (FUZZY LOGIC)             |      |

| FZINV: NEGATION ELEMENT (FUZZY LOGIC)                    |      |

| FZNAND: N INPUTS NAND ELEMENT (FUZZY LOGIC)              |      |

| FZNOR: N INPUTS NOR ELEMENT (FUZZY LOGIC)                |      |

| FZNOT: NEGATION ELEMENT (FUZZY LOGIC)                    |      |

| FZOR: N INPUTS OR ELEMENT (FUZZY LOGIC)                  | 106  |

| FZXNOR: 2 INPUTS XNOR ELEMENT (FUZZY LOGIC)              |      |

| FZXOR: 2 INPUTS XOR ELEMENT (FUZZY LOGIC)                |      |

| GAIN: GAIN ELEMENT                                       |      |

| GENERATOR: SUB CIRCUIT GENERATION FROM A FILE            |      |

| HOLD: HOLD AND TRACK ELEMENT                             |      |

| IALGEBRA: C EXPRESSION CAST TO INTEGER TYPE              |      |

| INTEGRATOR: NON INVERTING INTEGRATOR.                    |      |

| INV: NEGATION ELEMENT (BOOLEAN LOGIC)                    |      |

| ITOB: BIT EXTRACTOR FROM DIGITAL NODE                    |      |

| ITOD: CONVERTS A DIGITAL TYPE NODE TO ANALOG TYPE        |      |

|                                                          |      |

| ITOOL: USER-DEFINED TOOL                                 |      |

| IUSER: USER-DEFINED FUNCTION                             |      |

| LATCH: SR LATCH.                                         |      |

| LSHIFT: LEFT SHIFT ELEMENT                               |      |

| MAX: MAXIMUM OF N INPUTS                                 |      |

| MERGE: N INPUTS MULTIPLEXER FROM EXCLUSIVE LOOP SEGMENTS |      |

| MIN: MINIMUM OF N INPUTS                                 |      |

| MOD: MODULO DIVIDER ELEMENT                              |      |

| MULLER: C MULLER ELEMENT, N INPUTS (BOOLEAN LOGIC)       |      |

| MUX: N INPUTS MULTIPLEXER CONTROLLED BY INTEGER LEVELS   |      |

| NAND: N INPUTS NAND ELEMENT (BOOLEAN LOGIC)              |      |

| NOISE: SOURCE OF NOISE                                   |      |

| NOR: N INPUTS NOR ELEMENT (BOOLEAN LOGIC)                |      |

| NOT: NEGATION ELEMENT (BOOLEAN LOGIC)                    |      |

| OFFSET: DC LEVEL SHIFTER ELEMENT                         |      |

| OR: N INPUTS OR ELEMENT (BOOLEAN LOGIC)                  |      |

| OSC: OSCILLATOR                                          |      |

| POLY: POLYNOM OF ORDER N                                 |      |

| PROD: N INPUTS MULTIPLIER ELEMENT                        |      |

| QUANT: QUANTIFIER                                        |      |

| RAM: RANDOM ACCESS MEMORY                                | .117 |

| RAM2 DUAL PORT RANDOM ACCESS MEMORY                                           | 117                      |

|-------------------------------------------------------------------------------|--------------------------|

| RECT: RECTIFIER ELEMENT                                                       | 118                      |

| REGISTER: DATA REGISTER                                                       | 118                      |

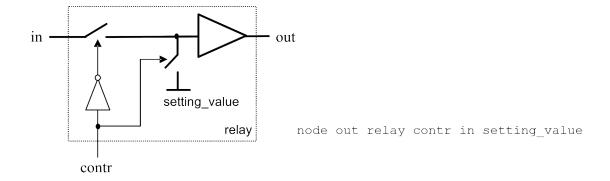

| RELAY: ONE INPUT RELAY, NORMALLY CLOSED                                       | 118                      |

| RIP: BIT WISE RIP BUS                                                         | 119                      |

| ROM: READ ONLY MEMORY                                                         | 119                      |

| ROM2: DUAL PORT READ ONLY MEMORY                                              | 120                      |

| RSHIFT: RIGHT SHIFT ELEMENT WITHOUT ROUNDING                                  | 120                      |

| RSHIFT1: RIGHT SHIFT ELEMENT WITH ROUNDING                                    | 121                      |

| RSHIFT2: RIGHT SHIFT ELEMENT WITH SPECIAL ROUNDING                            | 121                      |

| SIGN: SIGN OF SIGNAL                                                          | 121                      |

| SINE: SINE WAVE VOLTAGE GENERATOR.                                            | 121                      |

| SQUARE: SQUARE VOLTAGE SOURCE                                                 | 122                      |

| STEP: STEP FUNCTION SOURCE                                                    |                          |

| SUB: SUBTRACTION ELEMENT                                                      | 122                      |

| SUM: N INPUTS SUMMING ELEMENT                                                 | 123                      |

| TOGGLE: TOGGLE FLIP FLOP                                                      | 123                      |

| TEST: C EXPRESSION CAST TO INTEGER TYPE                                       | 123                      |

| TRACK: TRACK AND HOLD ELEMENT                                                 | 124                      |

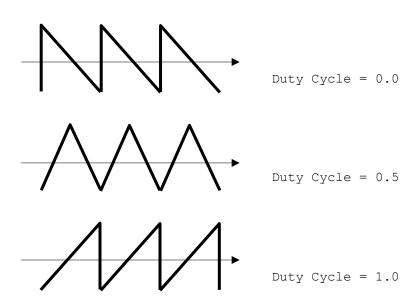

| TRIANGLE: TRIANGULAR VOLTAGE SOURCE                                           | 124                      |

| TRIG: TRIGGER (DUAL, POSITIVE OR NEGATIVE EDGE TRIGGER)                       | 125                      |

| UADC: N LEVELS UNSIGNED A/D CONVERTER                                         |                          |

| UDAC: N LEVELS UNSIGNED D/A CONVERTER                                         |                          |

| WSUM: WEIGHTED SUM OF N INPUTS                                                | 126                      |

| XNOR: N INPUTS XNOR ELEMENT (BOOLEAN LOGIC)                                   | 126                      |

| XOR: N INPUTS XOR ELEMENT (BOOLEAN LOGIC)                                     |                          |

| ZERO: INSERTION OF ZEROES.                                                    |                          |

| NAPA CONSTANTS AND TYPES                                                      | 120                      |

|                                                                               |                          |

| NAPA CONSTANTS                                                                |                          |

| CONSTANT TYPES                                                                |                          |

| GENERIC TYPES AND OUTPUT FORMATS                                              | 132                      |

| GLOBAL VARIABLES                                                              | 133                      |

|                                                                               |                          |

| NAPA C FUNCTIONS AND MACRO FUNCTIONS                                          | 135                      |

| AVAILABLE C MACRO FUNCTIONS                                                   | 125                      |

| AVAILABLE C MACRO FUNCTIONS                                                   |                          |

|                                                                               |                          |

| USER'S C FUNCTIONS                                                            | 139                      |

| USER-DEFINED FUNCTIONS AND TOOLS                                              | 140                      |

| THE CONCEPT                                                                   | 140                      |

| TOOL SYNCHRONIZATION.                                                         |                          |

| AN EXAMPLE OF TOOL                                                            |                          |

| RESOURCES MANAGERS                                                            |                          |

|                                                                               |                          |

| APPENDIX A                                                                    |                          |

| ALL ENDIA A                                                                   | 149                      |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION.                                     |                          |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION                                      | 149                      |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION                                      | 149<br>149               |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION                                      | 149<br>149<br>149        |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION Initialization Main Loop Termination | 149<br>149<br>149        |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION                                      | 149<br>149<br>149        |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION Initialization Main Loop Termination | 149<br>149<br>149<br>151 |

| NAPA SIMULATION FLOW. ORDER OF EXECUTION                                      | 149149149151             |

| NAPA FILE NAMING RECOMMENDATION       | 161 |

|---------------------------------------|-----|

| APPENDIX D                            | 162 |

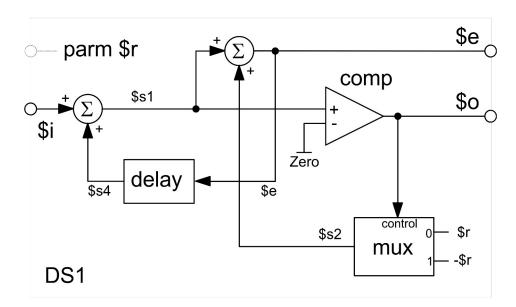

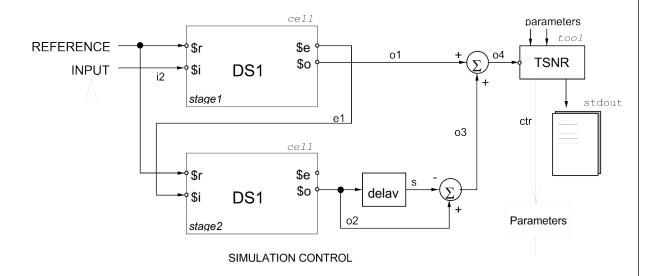

| NAPA NETLIST EXAMPLE                  | 162 |

| APPENDIX E                            | 167 |

| QUICK REFERENCE: NAPA INSTRUCTIONS    | 167 |

| APPENDIX F                            | 170 |

| QUICK REFERENCE: NODE SYNTAX          | 170 |

| APPENDIX G                            | 175 |

| QUICK REFERENCE: THE NAPA FILE SYSTEM | 175 |

# Introduction

**NAPA** offers a comprehensive work frame to IC designers for the high level simulation of complex mixed signals network.

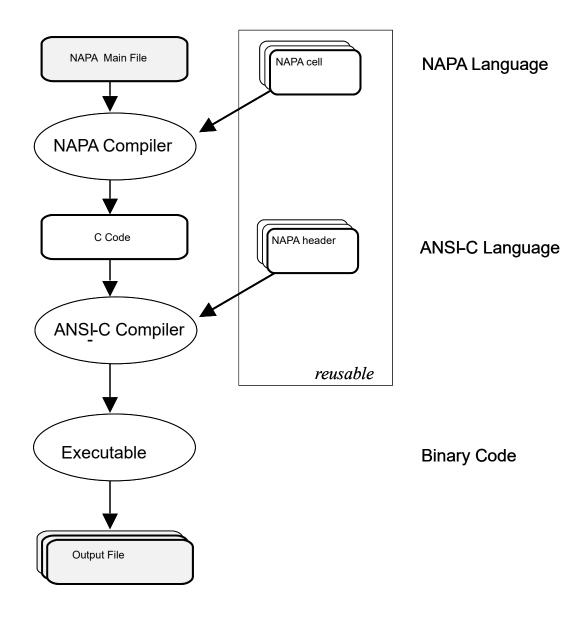

## The NAPA Compiler

**NAPA** is a netlist to **C** compiler. **NAPA** generates an optimized **Cycle Based Simulator**, which is compiled and executed. The goal is to offer a framework to describe quickly and safely a mixed-mode sampled data network with minimal constraints. The strategy used by NAPA is to help the designer produce the fastest possible **C** program to simulate a netlist without worrying about the complexities of actual **C** programming.

Just as an electrical circuit can be modeled as a set of differential equations, a discrete time network, like an analog modulator or a digital filter, can be modeled as a set of difference equations. The process of converting a netlist into a set of difference equations is straightforward and the perfect type of job for a computer.

*NAPA* reads in a netlist and writes out an optimized *ANSI-C* program. The output *C* program is combined with pre-written *C* program header files containing user-defined functions.

The C simulator written by NAPA uses "long long integer" and "double precision" respectively as internal representations of digital and analog nodes. Register arithmetic emulation allows simulation of the exact implementation of digital circuits if needed. Node types are determined automatically by netlist analysis and object determination. Type consistency is checked during simulator building.

**NAPA** is designed to be easily extended by users. Users can build high-level models and introduce them as header files, cells, or cell generators. Signal analysis is performed using synchronized "smart tools" that can accumulate the data necessary for analysis, open and close output files, while controlling the simulation flow. Tools are written in **C** and are designed to be modified, extended, or rewritten by users if necessary.

**NAPA** takes advantage of **ANSI-C**'s better consistency to catch errors. It also has an extensive set of verifications capable of detecting errors and unwanted casting in the netlist description. **NAPA** can be used advantageously with a data preprocessor like **MAC**. This preprocessor prepares the netlist, adding user-friendliness, documentation, and flexibility to the description.

**NAPA** currently runs on UNIX platforms like HP and Sun, and on PC-x86 platforms DOS and Windows<sup>1</sup>, with the only requirement being access to an **ANSI-C** compiler. The code is written to be as portable as possible and adheres to the **ANSI-C** standard.

<sup>1</sup> The environment used by the developper

### **NAPA** Identifiers

*NAPA*, like *C*, is case sensitive. *NAPA* identifiers must begin with a letter followed by zero or more alphanumeric characters (including the underscore character). *Identifiers starting with the prefix "NAPA"* are reserved keywords. Characters "\$" and "#" have special meaning and should be reserved for this purpose only. A complete list of *NAPA* identifiers and reserved keywords is given in appendix B. Reserved keywords cannot be used as *NAPA* node or variable identifiers.

```

Examples of valid identifiers:

s1

id

Sig12a

name_3B

```

# **NAPA** Iterative Identifiers

An iterative identifier is an identifier ending with "N..M" where N and M are positive integers. It replaces a sequence of identifiers with the same root followed by an integer between N and M. This helps keep the *NAPA* netlist as compact and readable as possible.

```

Example of valid iterative identifiers:

abc3..7

file2..0

```

These iterative identifiers (if accepted by the context) are equivalent to:

```

abc3 abc4 abc5 abc6 abc7 file2 file1 file0

```

There is another way to iterate nodes. Please refer to 'nodesets'.

### **NAPA** Instructions

A *NAPA* netlist is a sequence of one-line instructions. It is nevertheless possible to extend an instruction across several lines using a continuation character (see below). An instruction is identified by a keyword which must be the first token of the line. Depending on the instruction type, zero or more parameters follow the instruction identifier. The parameters of an instruction are identified by their positions.

#### <instruction\_keyword> [ <parameter...> ]

Instructions belong to five classes: declaration, action, control, input/output, and format, corresponding to the usual features available in programming languages. *NAPA* instructions can be location dependent. A list of instructions is given in a chapter below.

An instruction can be extended across several lines using the continuation character '...' at the end of all lines to be extended:

# <beginning\_of\_an\_instruction> <continuation\_of\_the\_instruction>

A continuation character is not active inside a string (delimited by double quotes). An example of an instruction spread across several lines is shown below (see also the paragraph about comments below):

```

node out dalgebra 1.0 ...

+ 2.0*in ...

+ 3.0*in*in

```

This is identical to:

```

node out dalgebra 1.0 + 2.0*in + 3.0*in*in

```

### Comments

*NAPA* supports 2 types of comments: whole line comment<sup>2</sup> and right-hand comment. Please note that C comment ( $/* \dots */$ ) is <u>not</u> supported.

# this is a whole line of comment

#### #\* this is a whole line of comment

<some relevant NAPA netlist line> // this is a right-hand comment

```

# This is an example of a whole line of comment

node w8 dc (digital) 255 // comment here if you want

```

Of course, a right-end comment is not active inside a string (delimited by double quotes). It is interesting to note that comments are compatible with continuation characters:

```

node out dalgebra 1.0 ... // offset term + 2.0*in ... // linear gain + 3.0*in*in // quadratic term

```

### **Nodes or Variables?**

To describe a system, you will mainly use the *NAPA* "node". The nodes represent the structure of the modules, both the signals and their fabrication. Parameters are introduced with another kind of basic instruction, "*ivar*" and "*dvar*". These parameters are the preferred way to describe the external world. Parameters are defined by default as constants but may be updated explicitly using dedicated instructions.

**An Example:** The gain of an amplifier is a parameter, determined by the (external) specifications of the module. It is preferable to use an "*ivar*" or a "*dvar*" to introduce this parameter. But if the gain of a gain-controlled amplifier depends on the states of the system, it will be defined as a "*node*" as it is a signal part of the structure of the system.

**Note:** On some occasions, you will have difficulty choosing. You will very often find that either the "node" or the "ivar" / "dvar" will give a cleaner description.

# The Concept of NAPA

The goal of this chapter is to give users an in-depth view of the NAPA compiler. A good way to understand the concept is to compare the NAPA input netlist with the ANSI-C output code produced by the compiler.

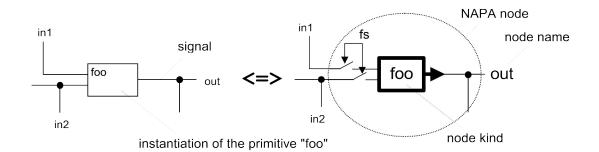

### The NAPA Node

node name

node out foo in1 in2

keyword

inputs or parameters

The network is built from UNIDIRECTIONAL primitives having one output and one or more inputs. Inputs are SAMPLED at a defined sampling frequency. These primitives associating an output node with the instantiation of an object (a primitive) are called *NAPA* nodes. Therefore, a *NAPA* node cannot be the output of two primitives and for this reason cannot be defined twice in a netlist.

An important point about nodes is that they are represented internally as either a double precision value (analog nodes) or a long long integer value (digital nodes). Some nodes are always analog or always digital type while others can be either, depending on how they are used or connected together.

### The NAPA Netlist

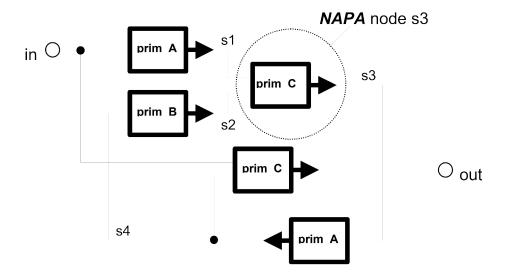

The *NAPA* netlist is the description of the circuit to be simulated. Considering, for example, the primitives called "prim\_A", "prim\_B" and "prim\_C" inside the following circuit:

The network can be translated in the *NAPA* netlist as a set of *NAPA* nodes:

```

node s3 prim_C s1 s2

node s1 prim_A in

node s2 prim_B s4

node s4 prim_A s3

node out prim_C in s4

...

```

The netlist is evaluated at a regular rate chosen by the user. Data are sampled by default at 1.0 Hz. This sampling frequency can be set-up by the user.

# The Sampling Frequency

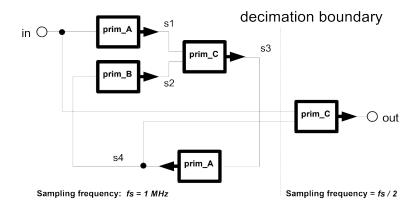

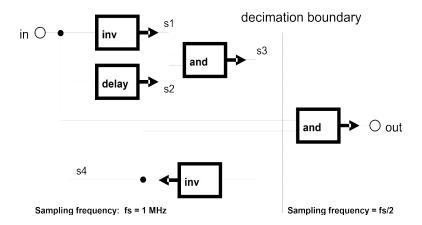

The *NAPA* compiler is designed to generate simulators for mixed signals sampled data networks. A main sampling frequency determines the pace of the simulation. Local sampling frequency can be decreased ('downsampling' or 'decimation') or increased ('upsampling' or 'interpolation'), depending on specific *NAPA* instructions. This feature is especially interesting in the description of digital filters. Considering the previous example, we can imagine that part of the network is running at half the main sampling frequency:

**NAPA** instruction "fs" defines the main sampling frequency. The decimation boundary separates the network into two separate segments. This separation is translated in the netlist by the instruction "decimate". This instruction decreases the sampling frequency of the second segment by the decimation factor (here a decimation factor of 2):

```

fs 1.0e6 // main sampling frequency

node s3 prim_C s1 s2 // part running at 1 MHz

node s1 prim_A in

node s2 prim_B s4

node s4 prim_A s3

decimate 2

node out prim_C in s4 // part running at 0.5 MHz

...

```

Interpolation follows the same principle. The interpolated rate is higher that the nominal sampling frequency, in the following example by a factor 16 (instruction "interpolate"):

```

fs 1.0e6 // main sampling frequency

node s3 prim_C s1 s2 // part running at 1 MHz

node s1 prim_A in

node s2 prim_B s4

node s4 prim_A s3

interpolate 16

node out prim_C in s4 // part running at 16 MHz

...

```

The description has to be completed by simulation controls and by other parameters controlling the way data are analyzed and output.

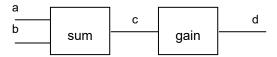

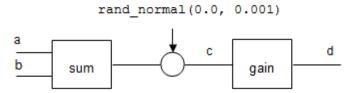

# The Netlist Processing

The *NAPA* compiler has the task of organizing and verifying the data flow of the sampled network, introducing delays where the user requests, without introducing any other delay. While processing the netlist, *NAPA* determines and verifies the node type (analog or digital) by inspection and sorting. *NAPA* also verifies that internal loops contain at least one delay (see the node determination).

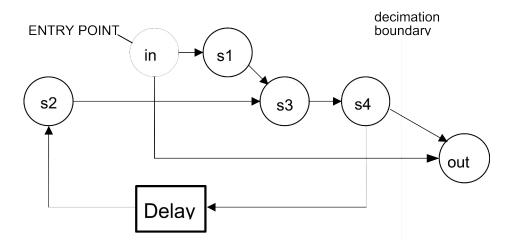

We will consider the following example:

The NAPA netlist corresponding to this network is:

```

. . .

fs

1.0e6

// main sampling frequency

node s3

and

s1 s2

// and gate

node s1

inv

in

// inverting gate

delay s4

// delay element

node s2

// inverting gate

node s4

inv

s3

node in

(to be completed)

// input signal

decimate 2

// decimation by 2

node out and

in s4

// and gate

```

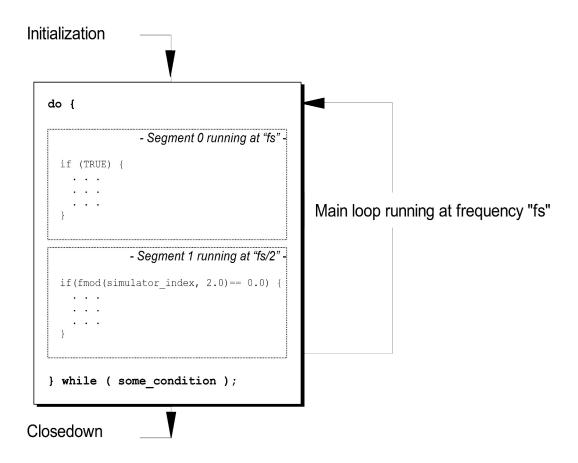

**NAPA** organizes the simulation around a main loop describing the data flow occurring inside one sampling cycle "1 / fs". The netlist is divided by decimation and interpolation instructions into segments, with the main segment being segment 0. Decimated and interpolated segments are introduced inside the main loop as "if" **C** instructions.

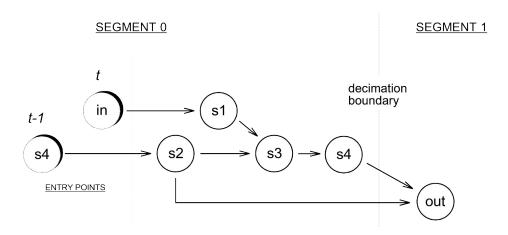

The compiler sorts the nodes of the entire netlist. In the example, segment 0 will contain the set of nodes running at the nominal sampling frequency "fs", and segment 1 will contain the nodes running at the decimated speed, here "fs / 2". Segment 0 contains nodes "s3", "s1", "s2", "s4" and "in". Segment 1 contains the node "out".

Some nodes (output of signal generators) are clearly not dependent on any other nodes. They are therefore unconditionally determined and are the entry points of the simulation. Delays represent a special class of nodes, as they are not dependent on a value at the current time but one simulation loop before.

The node tree corresponding to the netlist of the example is:

This tree corresponds to the following table:

| SEGMENT | ACTION CLASS     | DEPENDENCY | DETERMINED? |

|---------|------------------|------------|-------------|

| [0]     | immediate action | s1, s2     | ?           |

|         | immediate action | in         | ?           |

|         | delayed action   | s4         | ?           |

|         | immediate action | s3         | ?           |

|         | immediate action | (none)     | yes         |

| [1]     | immediate action | in, s4     | ?           |

# **Handling the Delays**

Delayed action nodes are processed first. New entry points are inserted for each delayed node at the beginning of corresponding segments. The entry points do not belong to the segment but are the entry points of the whole set of nodes of this segment. They represent the bridges between two consecutive simulation loops. A delay brings the value taken by a node from one loop into the next one.

After insertion of new entry points corresponding to delays (here for node "s4"), the tree becomes:

# **Node Determination and Sorting**

Nodes are sorted and their determination is checked by automatic netlist inspection. Entry points corresponding to delays are sorted first. All entry points are considered as unconditionally determined.

Other nodes are determined as soon as their inputs are determined. In the example, node "s1" is determined, as its input node "in" is determined.

At this point of the process, residual internal loops of nodes cannot be determined in any way. Therefore they are flagged as errors by the *NAPA* compiler. They correspond in the original *NAPA* netlist to loops without delay. This is a typical cause of node undetermination.

Node types (analog or digital) are obtained from node kinds and/or primitive input nodes. In the example, node "in" is supposed to be digital type by construction; node "s2" is integer type as it is the delayed image of node "s4" which is digital type by construction (output of an inverting gate).

| SEGMENT | NODE | ACTION CLASS     | DETERMINED? | ТҮРЕ         |

|---------|------|------------------|-------------|--------------|

| [0]     | s2   | delayed action   | yes         | Digital type |

|         |      |                  |             |              |

|         | in   | immediate action | yes         | Digital type |

|         | s1   | immediate action | yes         | Digital type |

|         | s3   | immediate action | yes         | Digital type |

|         | s4   | immediate action | yes         | Digital type |

| [1]     | out  | immediate action | yes         | Digital type |

Type consistency is checked during node determination.

### The Netlist to C Translation

From the processed list of nodes, the NAPA compiler translates the netlist into C code. The resultant code is a flattened description of the netlist without function calls.

```

. . .

double

NAPA simulator index;

long long inode s2;

long long inode in;

long long inode s1;

long long inode s3;

long long inode s4;

long long inode out;

int main(void) {

/* initialization

NAPA reset nodes();

/* loop counter

NAPA abs loop index = OLL;

/* main loop

NAPA time = ...;

/* always */ {

NAPA segment = 0;

inode s2 = inode s4;

/* delay element

/* clock generation

inode in = \dots;

/* inverting gate

*/

inode s1 = !inode in;

inode s3 = inode s1 \&\& inode s2;

/* and gate

/* inverting gate

*/

inode s4 = !inode s3;

if (NAPA_abs_loop_index % 2LL == 0LL) {

/* decimate by 2

NAPA segment = 1;

inode out = inode in && inode s4;

/* and gate

NAPA abs loop index++;

} while ( some condition );

/* end of main loop

return EXIT SUCCESS;

```

Note that the position of the code generating the signal "inode\_s2" introduces naturally the specified delay, with other nodes having an immediate action. Code producing the signal "inode\_out" is placed in a separate segment and is effectively running at half the speed of the first part.

### **The Simulation Control**

The simulation is controlled with the help of variables. Variables are used to control sources (e.g. "dc", "sine", "...") to parametrize nodes ("gain", "clip", "...") and to control the simulation or the data flow. NAPA user-defined analysis tools (smart tools) are especially built to take control of the simulation. The output node of a smart tool is a flag indicating the status of the ongoing process. Built-in synchronization mechanisms allow perfect synchronization between concurrent analysis tools. The simulation loop is controlled by a termination condition. For a complete example, see appendix D..

# NAPA in a Computer Network

*NAPA* output is generally directed to files. If a large volume of output is expected, it could be important that the simulation output does not travel across a network, especially if the network is slow.

The output stream could severely limit the speed of execution of the simulation. Avoid outputting too large amounts of data (especially to the screen), use an event condition to limit the amount of output, etc.

## **NAPA** Compiler Command Line

The *NAPA* command line requires one parameter and several options:

```

% NAPA_compiler_pathname <"input_source_file"> [ options ]

% NAPA_compiler_pathname < -help >

```

Where 'options' are:

```

-h[dr]

-n[et]

-g[en]

-d[ir]

-u[ser]

-header_directory_pathname

-d[ir]

-u[ser]

-ueader_directory_pathname

-uea

```

The input source file is a *NAPA* file containing the user's *NAPA* source and the library pathnames are respectively the pathnames of the directories "Hdr" ('-h' option), "Net" ('-n' option) and "Gen" ('-g' option). These directories contain the reusable headers, cells and cell generators. Defaults for these directories are respectively 'Hdr', 'Net' and 'Gen' referred to the generic directory pathname if mentioned by the '-d' option, otherwise referred to the current working directory.

The user name (with option '-u') will be added automatically to output files to complement the documentation. Any underscore in the user name will be replaced by a white space.

Scripts are available to launch the simulation in several environments (currently WINDOWS). They will not be described here as they can be heavily customized.

A second set of options provides information about the compiler:

**-a**[uthor]

### -b[uilt] -help

Three other options are possible,

- -I[ist]

- **-e**[xpand]

- -v[erbose]

The first one lists the nodes, variables and variable updates on the standard output. The location of the definition of each identifier is also output. No C file is generated. This option cannot be used in conjunction with '-e'.

The second one expands the source net files (main, cells and data cells) into a single expanded netlist on the standard output. The names of the identifiers are exactly the names produced during a regular compilation of *NAPA*. It helps to understand the expansion process and tracks the final identifier name generation. No *C* file is generated. This option cannot be used in conjunction with '-1'.

The last option switches the compiler to verbose mode. It details the compilation process somewhat and has limited interest for a regular user.

Several database organizations are possible; here is an example for a **DOS** platform:

| /home/ <i>NAPA</i> | $\begin{array}{c} \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \end{array}$ | /Simulate/NapaDos/Hdr<br>/Simulate/NapaDos/Net<br>/Simulate/NapaDos/Gen<br>/Simulate/NapaDos/Dos | contains generic header files contains generic cell files contains generic generator files contains <i>NAPA</i> compiler and scripts | (*.hdr)<br>(*.net)<br>(*.exe)     |

|--------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| /home/ jdoe        | $\rightarrow$                                                                                          | /jdoe/NAPA/project_1                                                                             | contains project's source files                                                                                                      | (*.nap)<br>(*.rom)                |

|                    |                                                                                                        |                                                                                                  | contains project's header files contains project's cell files                                                                        | <br>(*.hdr)<br>(*.net)<br>(*.dat) |

|                    |                                                                                                        |                                                                                                  | contains project's generator files                                                                                                   | (*.c)<br>(*exe)                   |

|                    |                                                                                                        |                                                                                                  | contains simulation output                                                                                                           | (*.out)                           |

|                    | $\rightarrow$                                                                                          | /jdoe/ <i>NAPA</i> /Hdr                                                                          | contains user's header files                                                                                                         | (*.hdr)                           |

|                    | $\rightarrow$                                                                                          | /jdoe/ <i>NAPA</i> /Net                                                                          | contains user's cell files                                                                                                           | (*.net)                           |

|                    |                                                                                                        |                                                                                                  |                                                                                                                                      | (*.dat)                           |

|                    | $\rightarrow$                                                                                          | /jdoe/ <i>NAPA</i> /Gen                                                                          | contains user's generator files                                                                                                      | (*.exe)<br>(*.c)                  |

To run *NAPA*, set the working directory to '/jdoe/NAPA/project 1'. Write for example in the command line:

Where 'NapaDos.exe' is the name of the *NAPA* compiler, 'gcc' is the *ANSI-C* compiler and 'myfile.nap' is the netlist to be simulated. Standard output of the simulator is redirected to 'myfile.out'. On other platforms, the command could be slightly different. As the *C* compiler has many options, it is particularly interesting to

choose carefully the optimization level. Optimizations reduce the execution time but could slow down the compilation significantly. Avoid hazardous optimizations, of course. Some tuning could be necessary.

Using a data macroprocessor like *MAC* (optional):

```

% /Simulate/MacDos/dos/MacDos.exe myfil.nap -c -l > myfil.tmp J

% /Simulate/NapaDos/dos/NapaDos.exe myfil.tmp -u "JDoe" -d /Simulate/NapaDos > myfile.c

J

% gcc myfil.c -o myfil.exe J

% myfil.exe > myfil.out J

```

Using the appropriate script, the command could be as simple as:

```

% NAPA myfile ↓

```

## **NAPA** Portability

*NAPA* is built to be portable. It is the user's responsibility to write new headers with *ANSI-C* syntax. It is also their responsibility to use file names compatible with WINDOWS and UNIX in order to ensure perfect compatibility of the netlists if needed. Some compatibility problems are expected on operating systems using different file naming conventions than UNIX.

*NAPA* runs on WINDOWS machines for instance if you use a GNU compiler, as the pathname conventions internal to the program follow the UNIX syntax.

# C limitations: Important Warnings!

In principle, *NAPA* is organized to get full access to *C* through several ports. Dedicated nodes ("const", "dc", "algebra", "ialgebra", "dalgebra" and "test"), variables ("dvar", "ivar", "update" and "event"), several instructions ("terminate", "drop", "assert"...) and conditional expressions ("...when") accept regular *C* expressions. Other nodes ("duser", "iuser", "dtool", "itool", "init", "call"...) trigger calls to *C* functions.

Some limitations are considered to avoid side effects.

The NAPA parser will reject the unary operators '++' and '--' inside a C expression placed in a NAPA netlist.

A *C* function placed in an expression of a *NAPA* netlist will be misinterpreted if it has the same name as a node or a variable. There are several specific checks but there are still some possibilities to have a name collision resulting in a *C* compiler error.

# C Casting: Important Warnings!

Although *ANSI-C* is safer than old *K&R C*, some potential problems remain. For instance, casting remains a potentially dangerous operation in *C* expressions:

Casting, first way to get unexpected results:

```

node a dc (digital) 5

node b dc (digital) 3

node c dalgebra a/b // cast to double by "dalgebra"

```

The resulting value of 'c' is 1.0, not 1.6667 as the integer division is applied before the casting. Every time it is possible, *NAPA* will refuse an integer number when a real number is expected. But the node "dalgebra" accepts a *C* expression. Nothing can be done to detect this potential problem.

#### Here you should prefer:

```

node a dc (digital) 5 // cast to digital node b dc (digital) 3 // cast to digital node c div a b

```

The resulting value of 'c' is now 1 as node "div" divide two digital nodes 'a' and 'b'. Clean and safe.

```

node a dc 5.0 // cast to analog node b dc 3.0 // cast to analog node c div a b

```

The resulting value of 'c' is now 1.6667 as node "div" divide two analog nodes 'a' and 'b'. Clean and safe.

Casting, a second way to get unexpected results:

```

node s1 dalgebra rand_uniform(-100.0, 100.0) // random noise node s2 ialgebra s1 // cast to long long int by 'ialgebra'

```

Histograms of 's2' show <u>twice</u> as much occurrences of 0 than any other numbers! Node "*ialgebra*" is making a *C* casting to long long int. Numbers between -0.9999 and 0.9999 produce 0! This is not what we were asking for!

Using dedicated *NAPA* primitives removes the problem:

```

node s1 dalgebra rand_uniform(-100.0, 100.0)  // random noise

node s2 dtoi s1

```

The node "dtoi" makes a perfect mathematical rounding. Only numbers between -0.4999.. and 0.4999.. produce 0.

### **NAPA Process Flow**

The simulator executable is generated through a two-stage compilation process:

- 1. **NAPA Compilation**: The NAPA compiler processes the netlist files and converts them into C source code

- 2. **C Compilation**: The ANSI-C compiler compiles the generated C code to produce the final executable simulator

This two-step process allows NAPA to leverage the optimization capabilities of standard C compilers while providing its own high-level simulation language.

## The NAPA File System

A NAPA netlist can be highly hierarchical. The compiler supports several pathname formats to locate files:

#### 1. Absolute Reference

Syntax: "/absolute/path"

Example: "/home/jdoe/examples/anycell.net"

#### 2. Generic Library Reference

Syntax: <filename>

**Examples:**

<wondertool.hdr> for headers in a header call

<wondercell.net> for cells in a cell call

<wondercell.gen> for generators in a generator call

tor

#### 3. Root Directory Reference

Syntax: "filename"

Example: "mydata.dat"

4. Main Directory Reference

Syntax: "~/filename"

Example: "~/mycell.net"

#### 5. Current Cell Directory Reference

Syntax: "./filename"

Example: "./mytool.hdr"

#### **Directory Definitions and Processing**

- **Generic Library**: Three specialized libraries containing reusable resources: the header library, the cell library, and the generator library. The pathnames of these directories are passed to the *NAPA* compiler through the command line.

- Generic library references are only valid when calling headers, cells, data cells, or generators.

- Root Directory: The working directory from which the NAPA compiler has been called.

- Main Directory: The directory containing the NAPA main netlist.

- Current Cell Directory: The directory containing the cell currently being processed.

The *NAPA* compiler processes pathname strings immediately and translates them into pathnames compatible with the operating system. To help the user, error messages will reference the operating system pathnames rather than the *NAPA* file system syntax.

#### **Best Practices**

Understanding the *NAPA* file system is essential when building netlists based on a set of files or directories. Using the appropriate reference types accurately ensures the ability to copy or relocate file sets while maintaining proper links between the data.

# **NAPA** Instructions

The NAPA instructions are divided in five classes: declaration, action, control, I/O and format.

The *NAPA* instructions are one-lined expressions. Keyword representing the expression is the first word of the line (there is one exception when using register arithmetic). Some of them are used in specific situations and are not of general interest (in *italic* below).

alias Declaration Declaration array Action assert Action call I/O command\_line Declaration comment data Declaration debug Declaration decimate control of simulation flow declare Declaration Declaration directive Control of simulation flow drop dump Action Declaration dvar Declaration error Declaration event

export I/O

format Output format

**fs** Declaration

**ganging** Declaration

gateway Control of simulation flow

**header** Declaration

init Actioninject Actioninput I/O

cell interface Declaration

data interface Declaration

**interlude** Declaration

interpolate Control of simulation flow

ivar Declaration

load Action

NAPA\_version Declaration

**node** Declaration

**nominal** Control of simulation flow

**opcode** Declaration

output I/O

ping Declaration

post Action

random\_seed Declaration

restart Action

**string** Declaration

stuck Declaration

synchronize Declaration

| terminate | Control of simulation flow |

|-----------|----------------------------|

| title     | Declaration                |

| tool      | Declaration                |

| ts        | Declaration                |

| update    | Action                     |

| void      | Declaration                |

| warning   | Declaration                |

# **NAPA** Nodes

The NAPA node is the key element of the netlist.

### **Usage**

A node is a *NAPA* object describing part of the netlist. Nodes are always defined as the output of an object (see chapter presenting the *NAPA* concept. The node is representing the object and its output signal together. It is generally not necessary to predeclare nodes. Internal loop of nodes in the netlist must include at least one delay. No node contains implicit delay, and "*delay*" nodes excepted (user defined nodes could contain delay(s), depending on the code implemented by the user!). *NAPA* sorts the nodes and determines the node types (analog or digital) after analysis of the netlist. The compiler is able to detect undetermined nodes, unauthorized loops, self-referencing node and wrong combination of node types.

Nodes are initialized by default, although user may modify their initialization (see instruction "init"). As initialization is an important issue, users are urged to read carefully initialization related NAPA documentation.

### node <node\_name> <kind> [ <parm...> ] [ <node\_name...> ]

In the generated C code, NAPA nodes are declared, defined and used with the prefix 'inode\_' or 'dnode' depending on the type: digital (long long integer) or analog (double precision). The NAPA nodes are translated as in-line C code to obtain better efficiency. This translation is context-dependent and is handled by the compiler. It means that the compiler handles the syntactic verification, declaration, initialization and code customization for the user.

*NAPA* is a strongly typed language. Nodes are represented in the simulator as

| analog node  | <i>NAPA</i> analog<br>type | (C double precision)          | prefix ' <i>dnode</i> _' |

|--------------|----------------------------|-------------------------------|--------------------------|

| digital node | <b>NAPA</b> digital type   | ( <b>C</b> long long integer) | prefix ' <i>inode_</i> ' |

### Chameleonic nodes

As often as possible, *NAPA* nodes have been implemented in such a way that they are conforming to the type of their inputs. Such nodes are called "**chameleonic nodes**". They can be used in both analog and digital context.

### **Nodesets**

A set of nodes may be defined in a single instruction. As the description could be more cryptic, it is recommended essentially to simplify the construction of generators.

```

node[4] out[2..5] sum in[4..1] in0

```

This is equivalent to the set of lines:

| node | out2 | sum | in4 | in0 |  |

|------|------|-----|-----|-----|--|

| node | out3 | sum | in3 | in0 |  |

| node | out4 | sum | in2 | in0 |  |

| node | out5 | sum | in1 | in0 |  |

Nodesets involving cell or generator are not authorized to avoid severe side effects. The declaration of width must match the iterators when they are used in the definition of the nodeset.

In the example above, the width is declared as 4 and the iterators have effectively the same width.

Other examples of application of the nodesets:

```

node[2] (out[1..2]) sum a1..4 b[4..5] // example with parenthesis

```

This is equivalent to the set of lines:

```

node (out1) sum a1 a2 a3 a4 b4

node (out2) sum a1 a2 a3 a4 b5

```

This example uses the concept to file names and variables:

```

ivar npts1 1000

ivar npts2 10000

node[2] void itool fft "file[1..2].out" in[4..5] ref npts[1..2]

```

This is equivalent to the set of lines:

```

ivar npts1  1000

ivar npts2  10000

node void itool fft "file1.out" in4 ref npts1

node void itool fft "file2.out" in5 ref npts2

```

### **Pseudo-Nodes**

Some nodes ("cell" and "generator") do not behave as true NAPA nodes. They are triggering the instantiation of a NAPA netlist. The syntax is depending directly to the way the "cell" (or the "generator") interface is written (see cell node). Although it is preferred to follow syntax similar to a regular node, with output on the left side and parameters and inputs on the right side, the user can define a cell with several outputs. As a regular node has only one output, the syntax must be changed: output nodes will figure also on the right hand:

```

node out1 cell mycel1 "cellfil1.net" out2 in1 in2 parm1

```

It is preferred and strongly recommended to use another syntax to stress the fact that the cell has multiple outputs by writing the cell interface differently:

```

node void cell mycel2 "cellfil2.net" out1 out2 parm1 in1 in2

```

The node 'void' is now corresponding to a dummy node in the cell netlist. See also paragraph below.

# **Unnamed and Unused Signals**

**NAPA** flags unused nodes or variables. To suppress the corresponding warning messages, a special identifier, "void" could be used as node or variable name. The simulator will attribute automatically an unambiguous and unique internal name for the corresponding **C** variable.

Another way to suppress the warning is to place the node or variable identifier in the definition between parentheses. The node or variable can therefore still be used. This is to be used with care as the absence of warning could hide a true error.

```

dvar (opt) 1.0 + b

node (err) sub out ref

node void itool fft "stdout" x 1.0 100000

```

Identifier "void" is used in the definition of node "mux" to define an empty input slot.

Identifier "void" is also used in the instruction "post" where it has a specific use, and is also a specific instruction.

### **Automatic Nodes**

To simplify the netlist, *NAPA* provides three "automatic nodes". The *NAPA* compiler automatically generates these nodes. It generates signals "One", "Zero" and "Ground" if it happens they are used in the netlist.

| One    | DIGITAL | constant value 1   |

|--------|---------|--------------------|

| Zero   | DIGITAL | constant value 0   |

| Ground | Analog  | constant value 0.0 |

The *NAPA* compiler processes these signals exactly as they were issued from normal DC nodes but THEY CANNOT BE DEFINED OR REDEFINED BY THE USER:

```

node One dc (digital) 1

node Zero dc (digital) 0

node Ground dc (analog) 0.0

```

## **Bit Field Extractor**

Single bit from any digital node can be accessed through the "bit field extractor". Respective nodes are automatically created to get the access. The notation is:

```

...<node_name> : <integer>...

```

The internal representation of a NAPA node or variable is based on the C "long long integer", i.e. 64 bits with 2 complement coding. Bit 0 is the least significant bit.

An example of bit field use:

```

node d4 sum d1 d2 d3

node d5 nand d2:4 d2:7 // to address 4th and 7th bits of d2

output "stdout" d4 d2:4 d2:5 d5

...

```

### **Node Kind List**

| NODE TYPE |          | BRIEF DESCRIPTION                              |                          |

|-----------|----------|------------------------------------------------|--------------------------|

| 1.        | adc      | N levels signed analog to digital converter    | $R \rightarrow I$        |

| 2.        | algebra  | generalized mathematical C expression          | Chameleonic              |

| 3.        | alu      | user-defined ALU                               | Chameleonic              |

| 4.        | and      | and of N input nodes (Boolean logic)           | $I \rightarrow I$        |

| 5.        | average  | Average of N input nodes                       | $R \rightarrow R$        |

| 6.        | bshift   | barrel shifter                                 | $I \rightarrow I$        |

| 7.        | btoi     | N bits to integer conversion                   | $I \rightarrow I$        |

| 8.        | buffer   | non inverting buffer (Boolean logic)           | $I \rightarrow I$        |

| 9.        | bwand    | bit wise and (Boolean logic)                   | $I \rightarrow I$        |

| 10.       | bwbuffer | bit wise non inverting buffer (Boolean logic)  | $I \rightarrow I$        |

| 11.       | bwinv    | bit wise inverter (Boolean logic)              | $I \rightarrow I$        |

| 12.       | bwnand   | bit wise nand (Boolean logic)                  | $I \rightarrow I$        |

| 13.       | bwnor    | bit wise nor (Boolean logic)                   | $I \rightarrow I$        |

| 14.       | bwnot    | strictly equivalent to "bwinv" (Boolean logic) | $I \rightarrow I$        |

| 15.       | bwor     | bit wise or (Boolean logic)                    | $I \rightarrow I$        |

| 16.       | bwxnor   | bit wise xnor (Boolean logic)                  | $I \rightarrow I$        |

| 17.       | bwxor    | bit wise xor (Boolean logic)                   | $I \rightarrow I$        |

| 18.       | cell     | sub circuit instantiation                      | Pseudo Node              |

| 19.       | change   | watchdog                                       | $X \rightarrow I$        |

| 20.       | clip     | clipping                                       | Chameleonic              |

| 21.       | clock    | clock generation (sequence of 0 and/or 1)      | $\rightarrow I$          |

| 22.       | comp     | comparator                                     | $X \rightarrow I$        |

| 23.       | const    | Constant with optional casting                 | $\rightarrow I \ or \ R$ |

| 24.       | copy     | signed copy                                    | Chameleonic              |

| 25.       | cosine   | cosine wave generator                          | $R \rightarrow R$        |

| 26.        | dac            | N levels signed digital to analog converter     | $I \rightarrow R$        |

|------------|----------------|-------------------------------------------------|--------------------------|

| 27.        | dalgebra       | generalized $C$ expression - casting to real    | $X \rightarrow R$        |

| 28.        | dc             | DC source with optional casting                 | $\rightarrow R \ or \ I$ |

| 29.        | delay          | simple or multiple delay                        | Chameleonic              |

| 30.        | differentiator | non delayed non inverting differentiator        | Chameleonic              |

| 31.        | div            | division of 2 input nodes                       | Chameleonic              |

| 32.        | dtoi           | real to integer conversion                      | $R \rightarrow I$        |

| 33.        | dtool          | equivalent to duser but not reset at restart    | $X \rightarrow R$        |

| 34.        | duser          | user-defined analog type function               | $X \rightarrow R$        |

| 35.        | equal          | equality of 2 input nodes                       | $X \rightarrow I$        |

| 36.        | fzand          | and of N input nodes (Fuzzy logic) <sup>2</sup> | $R \rightarrow R$        |

| 37.        | fzbuffer       | non inverting buffer (Fuzzy logic)              | $R \rightarrow R$        |

| 38.        | fzinv          | strictly equivalent to "fznot" (Fuzzy logic)    | $R \rightarrow R$        |

| 39.        | fznand         | nand of N input nodes (Fuzzy logic)             | $R \rightarrow R$        |

| 40.        | fznor          | nor of N input nodes (Fuzzy logic)              | $R \rightarrow R$        |

| 41.        | fznot          | negation of input node (Fuzzy logic)            | $R \rightarrow R$        |

| 42.        | fzor           | or of N input nodes (Fuzzy logic)               | $R \rightarrow R$        |

| 43.        | fzxnor         | xnor of 2 input nodes (Fuzzy logic)             | $R \rightarrow R$        |

| 44.        | fzxor          | xor of 2 input nodes (Fuzzy logic)              | $R \rightarrow R$        |

| 45.        | gain           | gain                                            | Chameleonic              |

| 46.        | generator      | sub circuit generation and instantiation        | Pseudo Node              |

| 47.        | hold           | hold (and track)                                | Chameleonic              |

| 48.        | ialgebra       | generalized $C$ expression - casting to integer | $X \rightarrow I$        |

| 49.        | integrator     | non delayed non inverting integrator            | Chameleonic              |

| <b>50.</b> | inv            | strictly equivalent to "not" (Boolean logic)    | $I \rightarrow I$        |

| 51.        | itob           | bit extractor from integer                      | $I \rightarrow I$        |

| 52.        | itod           | integer to real type conversion                 | $I \rightarrow R$        |

| 53.        | itool          | equivalent to iuser but not reset at restart    | $X \rightarrow I$        |

| 54.        | iuser          | user-defined digital type function              | $X \rightarrow I$        |

| 55.        | latch          | SR latch (Boolean logic)                        | $I \rightarrow I$        |

| 56.        | lshift         | left shift element                              | $I \rightarrow I$        |

| 57.        | max            | maximum of N input nodes                        | Chameleonic              |

| 58.        | merge          | merge N input nodes from exclusive segments     | Chameleonic              |

| 59.        | min            | minimum of N input nodes                        | Chameleonic              |

| 60.        | mod            | modulo division of 2 input nodes                | Chameleonic              |

| 61.        | muller         | C Muller, N input nodes (Boolean logic)         | $I \rightarrow I$        |

| 62.        | mux            | multiplexer (N inputs)                          | Chameleonic              |

| 63.        | nand           | nand of N input nodes (Boolean logic)           | $I \rightarrow I$        |

| 64.        | noise          | source of noise (normal)                        | $\rightarrow R$          |

| 65.        | nor            | nor of N input nodes (Boolean logic)            | $I \rightarrow I$        |

| 66.        | not            | negation of input node (Boolean logic)          | $I \rightarrow I$        |

| 67.        | offset         | DC level shifter                                | Chameleonic              |

| 68.        | or             | or of N input nodes (Boolean logic)             | $I \rightarrow I$        |

| <b>69.</b> | osc            | oscillator                                      | $R \to R$                |

|            | poly           | polynom of order N                              | Chameleonic              |

| 71.        | prod           | multiplier, product of N input nodes            | Chameleonic              |

<sup>2</sup> NAPA handles fuzzy logic gates (Zadeh operators) but has no other particular fuzzy logic intelligence.

| 72.        | quant    | quantifier                                      | Chameleonic       |

|------------|----------|-------------------------------------------------|-------------------|

| 73.        | ram      | random access memory                            | Declared          |

| 74.        | ram2     | dual port random access memory                  | Declared          |

| <i>75.</i> | rect     | rectifier                                       | Chameleonic       |

| <b>76.</b> | register | data register                                   | Chameleonic       |

| 77.        | relay    | relay, normally closed                          | Chameleonic       |

| <b>78.</b> | rip      | bit wise rip bus                                | $I \rightarrow I$ |

| <b>79.</b> | rom      | read only memory                                | Declared          |

| 80.        | rom2     | dual port read only memory                      | Declared          |

| 81.        | rshift   | right shift element without rounding            | $I \rightarrow I$ |

| 82.        | rshift1  | right shift element with rounding               | $I \rightarrow I$ |

| 83.        | rshift2  | right shift element with special rounding       | $I \rightarrow I$ |

| 84.        | sign     | sign of input                                   | $X \rightarrow I$ |

| 85.        | sine     | sine wave generator                             | $R \rightarrow R$ |

| 86.        | square   | square wave source                              | $\rightarrow R$   |

| <b>87.</b> | step     | step function source                            | $\rightarrow R$   |

| 88.        | sub      | subtraction of 2 input nodes                    | Chameleonic       |

| 89.        | sum      | sum of N input nodes                            | Chameleonic       |

| 90.        | test     | generalized $C$ expression - casting to integer | $X \rightarrow I$ |

| 91.        | toggle   | toggle flip-flop (Boolean logic)                | $I \rightarrow I$ |

| 92.        | track    | track (and hold)                                | Chameleonic       |

| 93.        | triangle | triangle wave source                            | $\rightarrow R$   |

| 94.        | trig     | trigger                                         | $X \rightarrow I$ |

| 95.        | uadc     | N levels unsigned analog to digital converter   | $R \rightarrow I$ |

| 96.        | udac     | N levels unsigned digital to analog converter   | $I \rightarrow R$ |

| <b>97.</b> | wsum     | weighted sum of N input nodes                   | Chameleonic       |

| 98.        | xnor     | exclusive nor of N input nodes (Boolean logic)  | $I \rightarrow I$ |

| 99.        | xor      | exclusive or of N input nodes (Boolean logic)   | $I \rightarrow I$ |

| 100.       | zero     | insertion of zeroes                             | Chameleonic       |

|            |          |                                                 |                   |

# **NAPA** User's Variables

A simulator is controlled by parameters. These parameters are not signals to process. In NAPA, they are called 'variables'.

# **Usage**

Besides nodes, one can specify user's variables. NAPA user's variables behave just like their C counterparts. Variables are not part of the node netlist description. They are used as object parameters or simulation control. Their declaration is mandatory. By default, the variables are not updated, but update is possible. The variable definition is a C expression possibly containing other variables, nodes or global variables. NAPA global variables are predefined in the generated C code and available to user. Self-referencing is not authorized in the definition of a variable but perfectly legal for an update:

```

dvar v1 v1 + v2 ILLEGAL!

ivar v3 0

update v3 v3 + 1

PERFECTLY OK

```

## Variable Type

Three types of user's variables are available: digital, analog or string variables. Variables are represented internally in the C simulator as:

| dvar   | <i>NAPA</i> analog type  | (C double precision)          | prefix ' <i>dvar_</i> ' |

|--------|--------------------------|-------------------------------|-------------------------|

| ivar   | <b>NAPA</b> digital type | ( <b>C</b> long long integer) | prefix ' <i>ivar</i> _' |

| string | <b>NAPA</b> string type  | (String of <b>C</b> char[])   | prefix ' <i>svar</i> _' |

The *NAPA* compiler handles register arithmetic, i.e. arithmetic performed on digital numbers coded with a limited number of bits..

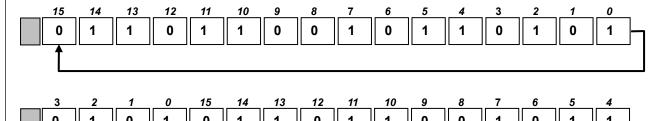

# **Register Arithmetic**

The simulation of digital filters requires to perform arithmetic on digital numbers coded with a limited number of bits.

### Width limited nodes and variables

Digital nodes and variables can be coded on a limited number of bits. Without any specific declaration, the *NAPA* compiler declares the digital nodes and variables as *ANSI-C* long long integer. Following *ANSI-C* standard, the "long long integer" is coded with a minimum of 64 bits. The *NAPA* compiler relies on the operators of the *C* compiler to perform the arithmetic and logic operations. It means that it is never straightforward to emulate a processor wider than 64 bits.

Nevertheless, it is possible to emulate the behavior of limited register width arithmetic by declaring the digital nodes or variables as width limited. Of course, it is not allowed to limit the coding of analog nodes and variables or to extend the coding of digital values to a number of bits beyond the "long long integer" size.

To limit the number of bits, it is necessary to declare the width of the nodes and the variables:

```

'('width')' "node" <nod_nam> <node_kind_returning_a_digital>...

'('width')' "ivar" <var_nam> ...

'<'width'>' "node" <nod_nam> <node_kind_returning_a_digital>...

'<'width'>' "ivar" <var_nam> ...

```

Where parenthesis applies for 2 COMPLEMENT SIGNED CODING. Angle brackets apply for UNSIGNED CODING.

```

(16)

// 2 complement 16 bits

node r1

gain

<16>

node r2

offset off b

// unsigned 16 bits

(16)

ivar m9

-9

// 2 complement 16 bits

<16>

ivar off

127

// unsigned 16 bits

```

Overflow is causing the proper ROLL-OFF particular to the coding, for example, when incrementing value 0 coded with 3 bits:

| 3 bits  | 2 complement | _ | 3 bits    | unsigned |   |

|---------|--------------|---|-----------|----------|---|

| 0002    | 010          |   | 0002      | 010      | _ |

| $001_2$ | 110          |   | $001_{2}$ | 110      |   |

| $010_2$ | 210          |   | $010_2$   | 210      |   |

| 0112    | 310          | _ | 0112      | 310      |   |

| 1002    | -410         | • | $100_2$   | 410      |   |

| $101_2$ | -310         |   | $101_2$   | 510      |   |

| $110_2$ | -210         |   | $110_{2}$ | 610      |   |

| 1112    | -110         |   | 1112      | 710      |   |

| $000_2$ | $O_{10}$     |   | 0002      | 010      |   |

| $001_2$ | 110          |   | 0012      | 110      |   |

|         |              |   |           |          |   |

**NAPA** handles a high level concept of the number, i.e. the decimal representation coded as a "long long integer". The result of a high level operation like "min" or "max" has not the same meaning to a 2 complement or an unsigned number. It means that the user must take care to choose the proper coding.